# КЛЮЧЕВЫЕ МОМЕНТЫ ТЕСТОПРИГОДНОЙ РАЗРАБОТКИ

АЛЕКСЕЙ ИВАНОВ, техн. консультант, JTAG Technologies

В этой статье идет речь о принципах тестопригодной разработки (DFT — Design-For-Testability) с учетом технологии периферийного (граничного) сканирования для последующего производственного и опытного тестирования плат. До сих пор многие разработчики воспринимают ЈТАБ как метод локальной верификации соединений или способ программирования ПЗУ и ПЛИС, а не как полноценный тестовый метод для выявления разнообразных дефектов. Между тем, JTAG давно уже «вырос» из примитивного подручного средства «прозвонки» и позволяет проверять цепи устройств памяти, связующей логики, разъемов, интерфейсных устройств. Статья знакомит читателя с «классическим» набором правил тестопригодной разработки, проиллюстрированных практическими примерами и пояснениями.

#### выбор компонентов

На первый взгляд, все просто: выбирать следует компоненты с поддержкой JTAG. Однако на практике бывает, что производители микросхем указывают в спецификации (datasheet) наличие JTAG-порта, но если изучить документацию более детально, оказывается, что он реализован только для целей отладки, просто как интерфейс (чаще всего это указывается примерно как "JTAG-port (only) for debugging purposes"). Такой компонент, имея в своем составе JTAG-интерфейс, не поддерживает стандарт IEEE 1149.1. Этот стандарт обязывает микросхему содержать несколько регистров, необходимых для тестирования плат, в том числе регистр периферийного сканирования, подключенный к внешним выводам микросхемы. При этом информация о соответствии стандарту в спецификациях (datasheet) может иметь различный вид — от одной строчки до целого раздела. Ключевыми словами, указывающими на то, что у микросхемы имеется полноценная тестовая логика, могут быть: "IEEE 1149.1", "boundary-scan", "JTAG for board testing" и т.п. Однако бывает и так, что микросхема полностью поддерживает тестирование по IEEE 1149.1, хотя в datasheet указывается лишь "JTAG-interface", и ничего более. Но это скорее исключение из правил, и встречается у отдельных производителей в сокращенных datasheet. В подробных руководствах указание на соответствие стандарту все-таки присутствует.

Одним из верных признаков того, что микросхема полностью поддерживает стандарт IEEE 1149.1, является наличие BSDL-файла, который описывает структуру необходимых регистров и, в частности, функции ячеек периферий-

ного сканирования для тестирования платы (вход, выход, управление). Файлы BSDL вместе со списками соединений из САПР составляют основу при автоматической генерации всех тестов и приложений. В большинстве случаев эти файлы можно загрузить с сайтов производителей микросхем. Правда, отдельные производители закрывают доступ к данной информации и поставляют BSDL только напрямую пользователям своих продуктов.

BSDL-файл бывает полезен при тестопригодном проектировании, так как многие производители компонентов с поддержкой стандарта IEEE 1149.1 добавляют в него полезные комментарии. Такие комментарии могут, например, содержать информацию о требуемых состояниях на определенных выводах для поддержания устройства в тестовом режиме во время тестирования. Изучение BSDL-файла при выборе компонентов также может указать на качество тестового покрытия будущей разработки. Ниже приведен отрывок из BSDL-файла, в котором описывается функциональность выводов устройства в режиме сканирования:

TINOUTO : inout bit;

CLKRO : inout bit;

FSRO : inout bit;

DRO : in bit;

CLKXO : inout bit;

FSXO : inout bit;

DXO : out bit;

RTCINX1 : linkage bit;

Здесь linkage bit означает вывод без поддержки сканирования, in (или out) bit говорит о том, что вывод во время тестирования будет однонаправленным, inout bit — двунаправленным. Чем больше у микросхемы выводов с

атрибутом inout bit, тем большим будет покрытие возможных неисправностей на плате; in и out лучше, чем ничего, однако возможностей уже не так много, поскольку вывод во время тестирования будет выполнять только роль выхода или входа. Следует заметить, что разработчики устройств на ПЛИС должны беспокоиться здесь меньше всего, так как у подавляющего большинства ПЛИС все цифровые выводы всегда имеют атрибут inout bit.

### РАЗБИВКА КАНАЛОВ СКАНИРОВАНИЯ

Не существует однозначного ответа, выводить ли несколько каналов сканирования или объединять все компоненты с поддержкой периферийного сканирования в одну цепочку. Тем не менее, приведем несколько соображений, которые могут помочь разработчику разобраться в данном вопросе. При этом у нас найдутся доводы как в пользу объединения, так и против него.

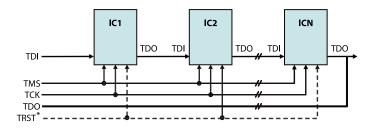

Некоторые разработчики считают объединение ТАР-сигналов в единую последовательную цепочку (см. рис. 1) лучшим и единственным решением, за исключением устройств с разными уровнями ТАР-сигналов или случаев, когда средства отладки не воспринимают «чужие» им устройства и требуют отдельного ЈТАG-канала. Такое объединение бывает не всегда необходимым и полезным, даже если на плате используются микросхемы одного производителя.

Разделение JTAG-компонентов в разные цепочки сканирования наиболее полезно с точки зрения сокращения длины тестовых векторов. Дело в том, что при создании тестов JTAG средствами проектирования на основе

Рис. 1. Объединение компонентов с JTAG в одну цепочку сканирования

Неиспользуемый сигнал от FPGA выключает данный элемент

Рис. 2. Управление отключением активных компонентов во время теста

анализа схематики генерируются так называемые векторы. Эти векторы (или паттерны) последовательно вдвигаются в ячейки регистров периферийного сканирования JTAG-микросхем и выставляются во внешние цепи. Затем результирующие последовательности, считанные с платы, выдвигаются обратно в тестовый контроллер. Таких векторов может быть от нескольких десятков при тестировании межкомпонентных соединений до нескольких тысяч при тестировании памяти типа DDR. С учетом того, что длина регистра периферийного сканирования современной ПЛИС может достигать 2—3 тысяч ячеек, можно представить длину общей последовательности для платы, солержащей несколько таких ПЛИС.

И хотя без разделения каналов даже при тестировании DDR-памяти время не будет астрономически велико, однако когда дело доходит до программирования флэш-ПЗУ, длина вектора становится важным фактором в ускорении процесса «прожига». Ведь такие устройства, как флэш-память, требуют значительно большего количества векторов; при этом все они так же подчиняются операции сдвига. Таким образом, разделение каналов важно не только для обеспечения работы «родных» отладочных средств устройств, но и, например, для обеспечения скоростного «прожига» ЭСПЗУ на тестируемой плате. При этом следует заметить: средства JTAG-тестирования чаще всего допускают включение в одну цепочку микросхем разных производителей.

Противоположный подход — когда разработчик выводит порт каждой JTAG-микросхемы в отдельный канал со своим разъемом. При этом, прежде всего, увеличиваются габариты платы. Между тем многие современные JTAG-тестеры позволяют работать одновременно с несколькими ТАРпортами, а в случае необходимости можно использовать платы расширения, которые мультиплексируют JTAGканалы. Это помогло бы уменьшить число разъемов, однако разработчики зачастую вообще отказываются от применения JTAG для тестирования, используя интерфейс только на тех устройствах, где требуется конфигурирование, «прошивка» или отладка, замыкая JTAG-порты остальных микросхем на «землю», и тем самым значительно сокращая возможности тестового покрытия изделия в целом.

При этом вне тестового покрытия оказываются такие компоненты, у которых JTAG предназначен только для тестирования цепей платы, на которую они устанавливаются: например, интерфейсные микросхемы Ethernet, PCI, некоторые микросхемы оперативной памяти (в принципе, память при JTAG-тестировании не должна соответство-

вать стандарту IEEE 1149.1, так как для проверки связей с ОЗУ используются окружающие микросхемы, поддерживающие периферийное сканирование. Впрочем, некоторые производители чипов памяти военного и космического назначения встраивают тестовую логику JTAG для повышения надежности теста ответственных изделий).

Чтобы не снижать качество тестирования, можно объединить такие устройства в одну JTAG-цепочку, или даже включить их в каналы сканирования других устройств. Тогда на плату не нужно выводить много разъемов. При использовании средств отладки, не приемлющих «посторонних» устройств в цепочке, можно исключить их при помощи, например, джамперов или нулевых резисторов.

Итак, необходимо найти некий «баланс» при разбиении каналов сканирования, причем каждый конкретный проект нуждается в индивидуальном подходе в зависимости от требований к процессу тестирования, габаритов платы и других факторов. В идеале на сложных платах, содержащих большое количество JTAG-микросхем, должна быть проведена их логическая разгруппировка по нескольким каналам сканирования.

## КОНТРОЛЬ КОМПОНЕНТОВ БЕЗ ПОДДЕРЖКИ IEEE 1149.1

Одним из немаловажных аспектов тестопригодной разработки является контроль активных компонентов в процессе JTAG-тестирования. Речь идет о компонентах без поддержки периферийного сканирования или, как их еще называют, «кластерах». В роли таких «кластеров» могут выступать любые компоненты: память, логика, интерфейсные устройства, ЦАП и АЦП.

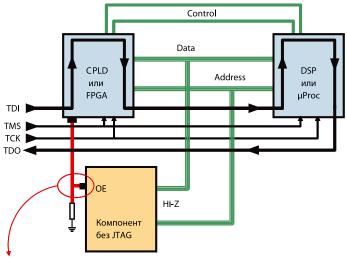

Предположим, что у нас есть схема, приведенная на рисунке 2. Для того чтобы в процессе тестирования получить наибольшее тестовое покрытие, нам требуется проверить цепи между процессором и ПЛИС, а также соединения каждого из них с третьим компонентом, который является «кластером». Поэтому тестирование данной схемы будет разбито на два этапа (из таких этапов затем создаются производственные тестовые последовательности).

Первый этап — это тестирование соединений между JTAG-компонентами: ПЛИС и процессором. Несмотря на то, что на данном этапе кроме проверки связей этих двух микросхем могут выявляться также некоторые дефекты и третьей (например, КЗ), требуется более тщательное тестирование цепей, идущих от JTAG-компонентов к «кластеру». Поэтому на втором этапе будет использоваться модель функционирования «класте-

Рис. 3. Контроль над синхронизацией со стороны тестовых векторов

ра», на основе которой будут генерироваться тестовые последовательности, выставляемые как с одной, так и с другой JTAG-микросхемы, а также словари для диагностирования дефектов. Но для выполнения первого этапа нам требуется, чтобы третий компонент был в пассивном состоянии и желательно, чтобы его выводы, которые волею случая оказались на общей шине, в это время находились в состоянии высокого импеданса.

Практика показывает, что распространенным является случай, когда подобный «кластер» имеет такую возможность перевода в третье состояние, однако разработчик жестко заводит сигнал управления (в нашем примере — ОЕ) на определенный уровень без возможности манипуляций с ним. При этом, скажем, у той же ПЛИС присутствует большое количество неиспользованных выводов. Неподключенные выводы JTAG-компонентов рекомендуется использовать для контроля остальной «периферии» на плате. Следует отметить, что при использовании сканирования тестовые векторы будут автоматически удерживать сигналы управления, а соответствующие биты для контрольных цепей будут содержаться в каждом из них.

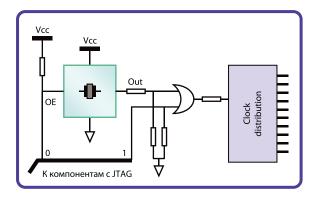

Вторая проблема с отсутствием контроля — это «неуправляемость» кварцевых резонаторов, используемых в тестируемой схеме. Сигнал от одного такого резонатора может распределяться по многим блокам схемы, и, если не обеспечить его отключение, можно потерять часть тестового покрытия платы. Во-первых, цепи сигналов синхронизации будут исключены из теста, и мы не сможем локализовать некоторые потенциальные неисправности на них (короткие замыкания, обрывы и т.д.). Во-вторых, некоторые «кластеры» управляются тактовыми сигналами: это могут быть устройства динамической памяти или определенные виды

Важно помнить, что для тестирования таких устройств при помощи периферийного сканирования необходимо обеспечить их контроль со стороны JTAG-компонентов; это касается и тактовых сигналов, которые будут «подменяться» при помощи тестовых векторов. Таким образом, управление отключением резонатора на практике может увеличить тестовое покрытие

платы на 10—20% благодаря включению в тест «кластеров», требующих для симуляции своей работы тактовых сигналов.

Вариантов реализации такой «подмены» может быть много, и, наверное, это тема отдельного разговора. На рисунке 3 показан один возможных способов. Данная схема позволяет во время тестирования одновременно отключать генератор и управлять синхронизацией, к примеру, блока динамической памяти, хотя ситуация могла быть неподконтрольной при соединении сигнала ОЕ генератора только с цепью питания. Заметим, что существуют распределители с ФАПЧ, где нижняя частота пропускаемых синхросигналов ограничена. Для периферийного сканирования, во время которого тактовые импульсы симулируются с помощью операций сдвига, такая граница может быть зачастую недостижима. Поэтому также рекомендуется выбирать распределители с возможностью отключения порога пропускания.

Автор надеется, что на нескольких приведенных примерах ему удалось не только осветить некоторые наиболее важные аспекты тестопригодного проектирования, но и ответить на вопрос о том, что дает в итоге выполнение таких рекомендаций.

### ЛИТЕРАТУРА

- 1. Руководство по разработке тестопригодных печатных плат//www.jtagtechnologies.ru.

- 2. Иванов А.В. Тестопригодность электронных изделий как залог успеха предприятия//Поверхностный монтаж, 2009, №4, с. 22–23.

- 3. Городецкий А., Курилан Л. Тестопригодное проектирование схем для граничного сканирования//Производство электроники, 2008, №1.

### НОВОСТИ СВЕТОТЕХНИКИ

### КОНФЕРЕНЦИЯ STRATEGIES IN LIGHT 2010 ОЗНАМЕНОВАЛА НАЧАЛО НОВОГО ЭТАПА РАЗВИТИЯ РЫНКА СВЕТОДИО-

ДОВ | Последняя, 11-я, конференция и выставка Strategies in Light 2010 была полна оптимизма в отношении прогнозируемого устойчивого роста рынка в ближайшие годы. После года резкого спада и последующего восстановления, в результате которого рост чистой выручки на рынке светодиодов высокой яркости в 2009 г. составил 5%, в настоящее время этот рынок переходит в новую фазу своего развития. Ожидается, что под влиянием возрастающего спроса со стороны таких приложений как подсветка ЖК-дисплеев и светодиодное освещение, рынок светодиодов вырастет в 2010 г. на более чем 50%. Эти позитивные данные были представлены участниками конференции.

11-я ежегодная конференция Strategies in Light 2010 проводилась в Санта-Клара (Калифорния) и включала две параллельные секции, на одной из которых обсуждался рынок светодиодов высокой яркости, а на другой — светодиодные системы освещения. В этом году новым на конференции стало проведение форума инвесторов по твердотельным системам освещения, во время которого свои технологии представили 12 компаний.

Регламент конференции включал проведение четырех семинаров и двух занятий. В работе конференции присутствовали 90 экспонентов и около 3000 зарегистрированных участников. Другим важным событием этого мероприятия стало объявление результатов конкурса по выбору лучшего светильника следующего поколения (Next Generation Luminaires).

www.russianelectronics.ru