## Периферийное сканирование в жизненном цикле изделия

**Алексей Иванов**, JTAG Technologies alexey@jtag.com

Журнал «Производство электроники» уже на протяжении нескольких лет публикует цикл статей, посвященный технологии граничного или периферийного сканирования. Однако сам предмет этих статей, его место на каждом этапе производственного цикла до сих пор не получил должного освещения. Исправляем ситуацию.

На прошедшем прошлой осенью форуме «Производство Электроники в России» многие участники в своих выступлениях довольно часто употребляли понятие «жизненный цикл изделия», подчеркивая при этом, что он не выполняется, как следует, или вовсе не учитывается. Что же при этом имелось в виду? Жизненный цикл изделия по стандарту ISO 9004-1 — это совокупность процессов, выполняемых от момента выявления потребностей общества в определенной продукции до момента удовлетворения этих потребностей и утилизации продукта. С точки зрения производства электроники сюда может входить разработка, опытное и серийное производство, ремонт и постпродажное сервисное обслуживание. Кроме прочего, в жизненный цикл должен включаться и маркетинг (от идеи до продажи изделия), но мы в этой статье остановимся только на технологических этапах. При проработке жизненного цикла (а его необходимо прорабатывать) очень важно избежать несоответствий между всеми этапами, сделать переход от одной стадии к другой «прозрачным» и гармоничным. Точно такая же ситуашия складывается и с тестированием. которое неизменно должно входить в данную проработку.

В настоящее время на российских предприятиях сложились два подхода к электрическому тестированию, которые никак не вписываются в вышеприведенные тезисы и не соответствуют нормам производства высокотехнологичной продукции.

Первый подход — это использование на производстве и при сервисном обслуживании функциональных проверок, созданных для отладки и верификации прототипов изделия разработчиками, довольно сложных

и трудоемких, не дающих абсолютно никакой локализации дефектов. Зачастую ТУ для опытного образца никак не отличается от ТУ для серийного изделия, порой включая даже проверку аппаратного программного обеспечения.

Второй подход — это использование автоматического тестирования (будь то структурное или функциональное). Однако инженеры, работающие на производстве, сталкиваются с проблемами отсутствия тестопригодной разработки. То есть, автоматическое тестирование не было учтено в жизненном цикле изделия, да и, скорее всего, жизненный цикл не рассматривался вообще. Основная проблема здесь — это то, что все составляющие жизненного цикла живут как бы «своей жизнью», откуда следует практически полное игнорирование таких принципов разработки, как DFM, DFT, DFQ и т.д.

Далее речь пойдет о том, как внедрение такой технологии, как периферийное сканирование, может помочь связать воедино все этапы жизненного пикла.

## **РАЗРАБОТКА**

Одним из преимуществ периферийного сканирования, как структурного тестового метода, является возможность его использования еще при разработке изделий. И возможность эта порождена самой технологией, которой не требуется внешний доступ к тестируемым цепям, а необходимо лишь наличие «виртуальных» пробников, находящихся внутри кристаллов используемых в изделии микросхем. Поэтому метод не зависит от топологии, расположения и наличия тестовых точек и т.д., что крайне важно, например, для внутрисхемного тестера.

Это преимущество дает возможность создавать тесты на основе схематики для самых «сырых» прототипов.

Нужно отметить, что тестирование опытных образцов очень важно не только с точки зрения облегчения жизни разработчика. Это также ускоряет процесс самой разработки, как одного из этапов жизненного цикла, благодаря тому, что позволяет быстро отделить производственные дефекты от ошибок разработки и заняться, собственно, отладкой нового продукта.

Теперь вспомним о таком понятии, как DFT (Design-for-Testability). Всем хорошо известно, с каким «энтузиазмом» разработчики выполняют требования «чего-угодно-пригодной» разработки. Но разработчик все же не всегда виноват в несоблюдении правил. Зачастую это происходит за отсутствием четких рекомендаций, инструментария и просто обучающих тренингов. И если для принципа DFM еще можно найти рекомендации, то для DFT очень редко. У компании JTAG Technologies имеется брошюра на русском языке «Руководство по тестопригодному проектированию печатных плат», однако она относится только к периферийному сканированию, а не ко всем видам тестирования.

Тем не менее, использование разработчиками электрического тестирования для своих опытных образцов имеет самые положительные последствия. Это мотивирует их создавать продукт, соответствующий современным правилам тестопригодной разработки, так как они лично могут этим тестированием воспользоваться.

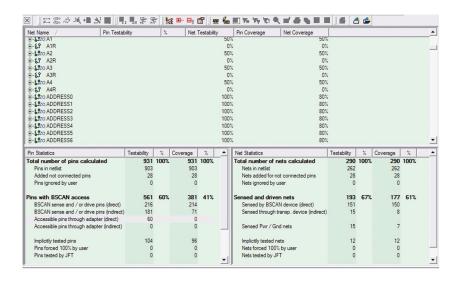

Кроме всего прочего, современные средства проектирования тестов позволяют рассчитывать тестовое покрытие будущего изделия, даже

Рис. 1. Табличное представление отчета о тестовом покрытии с детальной информацией по каждой цепи

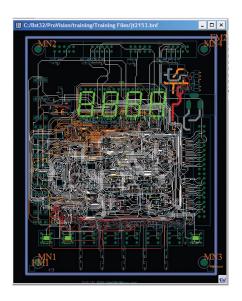

не имея «живого» образца. Как уже было упомянуто выше, системе периферийного сканирования нужна только схематика платы для разработки тестов и приложений. В дополнение к схематике требуется ввести информацию об используемых компонентах (в особенности тех, которые поддерживают периферийное сканирование). После этого система анализирует межкомпонентные связи и логику самих компонентов для генерации всевозможных тестов. Во время генерации также создается отчет о тестовом покрытии платы теоретическом и реально достигнутым. Система проектирования JTAG ProVision позволяет даже визуализировать отчет на схематике и, при наличии файлов разводки, на рисунке печатной платы. На рисунках 1 и 2 показано табличное представление расчета тестового покрытия платы и его визуализация на печатной плате. При этом цепи с разной степенью локализации дефектов помечены разным цветом. Таким образом, вмес-

Рис. 3. Один из первых контроллеров периферийного сканирования, находящийся в музее JTAG Technologies в г. Эйндховен (Нидерланды)

те с тестовым методом разработчик получает еще и инструменты расчета тестового покрытия. Дав разработчику все эти возможности, руководство имеет гораздо больше прав требовать от него выполнения условий DFT, который при недостаточном тестовом покрытии может внести изменения в схематику или компонентную базу, параллельно изменяя JTAG-проект и оперативно пересчитывая данные. А стратегия DFT, в свою очередь, является неотъемлемой частью жизненного пикла излелия.

## производство

Начнем с того, что стандарт периферийного сканирования (IEEE 1149.1) разрабатывался в 80-х годах в помощь производству. Это теперь JTAGинтерфейс используют и разработчики (причем как аппаратной, так и программной частей), и производство, и даже сервис-инженеры по ремонту импортной бытовой техники. Причем используют для всевозможных целей: программирование, эмуляция, тестирование, отладка и ремонт. Хотя создатели JTAG были нацелены именно на локализацию производственных дефектов. Инженеры, работавшие над стандартом, были выходцами из тестового подразделения Philips, из которого, собственно, затем образовалась компания JTAG Technologies. Первые производственные контроллеры, впоследствии выпускавшиеся JTAG Technologies, имели на себе фирменный знак «Philips» (см. рис. 3). Занималось данное подразделение ис-

Рис. 2. Визуальное представление тестового покрытия на рисунке печатной платы

ключительно производственным тестированием. И только потом, в 90-х годах, появились новые применения JTAG, как удобного в использовании интерфейса.

Каковы же области применения периферийного сканирования при производстве изделий? Прежде всего, следует отметить гибкость данного метода по отношению к серийности изделия. Скажем, для выполнения внутрисхемного контроля (если, конечно, это не установка с летающими пробниками) требуется создание специализированной оснастки. Оснастка для JTAG-теста — это один или несколько кабелей (в зависимости от сложности изделия). Поэтому данный метод можно применять как при производстве опытных образцов, так и при серийном производстве. Вообще говоря, сам JTAG-тестер не является таким уж громоздким как, например. установки внутрисхемного тестирования или рентгеновского контроля, поэтому он может размещаться непосредственно на участках регулировки и настройки, что является более привычным для российских предприятий, которые сами производят свою продукцию и где тестирование традиционно ассоциируется с функциональной проверкой.

Существует несколько вариантов организации рабочего места периферийного сканирования. Самый оптимальный вариант — это универсальная станция по тестированию, диагностике, программированию и функциональному контролю изделий. Все эти

операции можно совместить на базе одного ПК. В данном случае требуется всего лишь один оператор, последовательно запускающий все действия. На сегодняшний день предлагаются довольно обширные возможности интеграции JTAG-тестов в существующие программные средства. К примеру, у JTAG Technologies имеются следующие варианты «производственного» запуска приложений, созданных в среде проектирования JTAG ProVision:

- автономная станция AEX Manager («родной» секвенсор для запуска приложений JTAG Technologies);

- пакет интеграции для Visual Basic:

- пакет интеграции в C/C++ориентированные среды программирования;

- исполняемые модули (\*.exe) для

Windows и Unix:

- интеграция в LabVIEW, Lab-Windows и TestStand от National Instruments:

- система Symphony для интеграции в производственные тестеры различных производителей.

Благодаря всем этим пакетам интеграции можно не только запускать тесты и приложения для программирования, созданные на основе периферийного сканирования, но и наиболее полно использовать функции JTAG-тестеров, например, групповое тестирование и программирование нескольких плат, управление напряжением ТАР-сигналов и дополнительными сигналами. Не стоит забывать, однако, что станцию проектирования тестов также можно использовать для производственного тестирования в случаях, когда процесс разработки приложений не занимает слишком много времени.

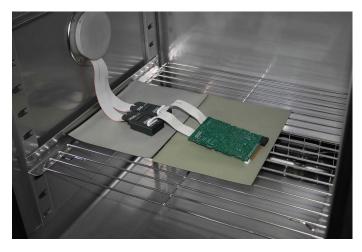

Следует отметить еще одну возможную область применения периферийного сканирования. Речь идет о климатических испытаниях. Как проводить диагностику изделия, которое отказывается работать при температуре -25°C? Результат некачественной пайки может проявляться на критических температурах, однако исчезать при комнатной. Очевидно, что данная проблема приносит большие неудобства, так как рентгеновский аппарат и внутрисхемный тестер не «засунешь» в климатическую камеру. Именно поэтому JTAGтестеры делаются с «выносными»

Рис. 4. Тестирование в климатической камере

оконечными согласующими устройствами ТАР-портов, удлиняемыми при помощи кабелей. При этом конечный адаптер выполняется в промышленном температурном диапазоне для того, чтобы его можно было поместить в термокамеру (см. рис. 4). Таким образом, для изделия, находящегося в условиях критических температур, можно проводить не только функциональный самоконтроль, но и электрическое тестирование, которое особенно эффективно в случае, когда вышеупомянутый «самоконтроль» попросту не запускается из-за возникающих дефектов.

## СЕРВИС И РЕМОНТ

Ни для кого не секрет, что JTAGинтерфейс активно используется для ремонта цифровой техники. Но применяется он в основном для перепрошивки ПЗУ, да и то сервисными центрами по ремонту мобильных устройств. Тем не менее, JTAG дает более широкие возможности в области ремонта и сервисного обслуживания изделий цифровой техники, и не только бытовой.

Всем известно, насколько неприятным бывает процесс ремонта и диагностики плат с влагозащитным покрытием. Во многих случаях приходится удалять лак полностью или частично, особенно если диагностика заключается в последовательной замене микросхем, вызывающих подозрение, после чего очень часто платы становятся неремонтопригодными или пригодными только для внутреннего использования на родном предприятии. Тестирование изделий с покрытием при помощи периферийного сканирования может позволить избежать заведомо неверных действий по демонтажу и перепайке, приводящих к их «гибели» платы.

То же самое относится к ремонту и тестированию блоков, состоящих из нескольких плат. Если обеспечить доступ к каналам сканирования находящихся внутри плат, то необязательно сразу же разбирать данный блок. Можно предварительно провести тестирование составляющих его плат, чтобы локализовать дефектные составляющие и избежать лишней работы. Если в послепродажном жизненном цикле платы внутри блока должны подвергаться частой перепрошивке (обновление аппаратного ПО), то следует задуматься о том, чтобы обеспечить легкий доступ к каналам JTAG и, возможно, даже объединить их в единую шину, находящуюся на кросс-плате.

В заключение хочется сказать: нет панацеи от всех бел. И периферийное сканирование таковым не является. Качество продукции зависит от многих факторов: квалификации кадров, правильных техпроцессов, логистики, управления, тестовой стратегии и т. д. Необходимо принимать во внимание и жизненный цикл продукции, состоящий из многих звеньев, которые в нашей стране в большинстве случаев между собой практически не связаны, из-за чего производство часто становится невыгодным. На примере одного из тестовых методов - периферийного сканирования по стандарту JTAG IEEE 1149.1 мы показали, как можно хотя бы в некоторых сферах связать воедино эти звенья и как сделать первый шаг к тестопригодной разработке.